# CMOS DIGITAL DATA BOOK

## Harris Semiconductor Sector Capabilities

Harris Semiconductor, one of the top ten U.S. merchant semiconductor suppliers, is a sector of Harris Corporation — a producer of advanced information processing, communication and microelectronic products for the worldwide information technology market.

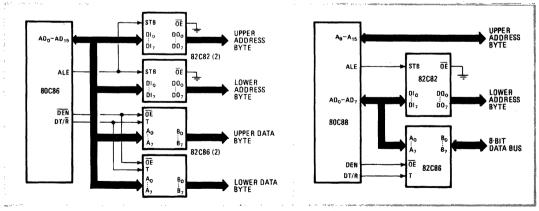

Harris Semiconductor is organized to address the standard products, custom products, and gallium arsenide semiconductor markets.

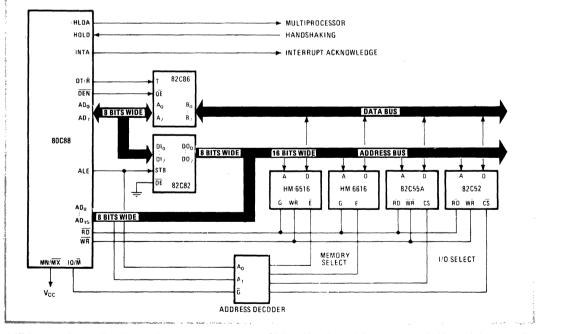

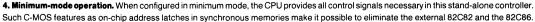

#### SEMICONDUCTOR PRODUCTS DIVISION

Harris Semiconductor offers a wide selection of standard analog and digital circuits through its Semiconductor Products Division:

#### Analog Products

Harris is a major force in analog integrated circuitry, offering a broad line of products including: analogto-digital converters, digital-to-analog converters, sample-and-hold circuits, multiplexers, switches, voltage references, operational amplifiers, telecommunications and speech processing products, hybrid subsystems and active filters. (See complete analog product listing, page 12-2.)

#### **Digital Products**

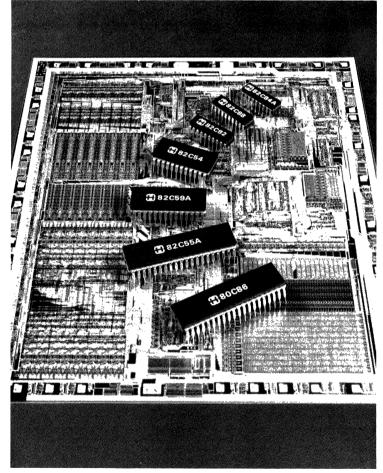

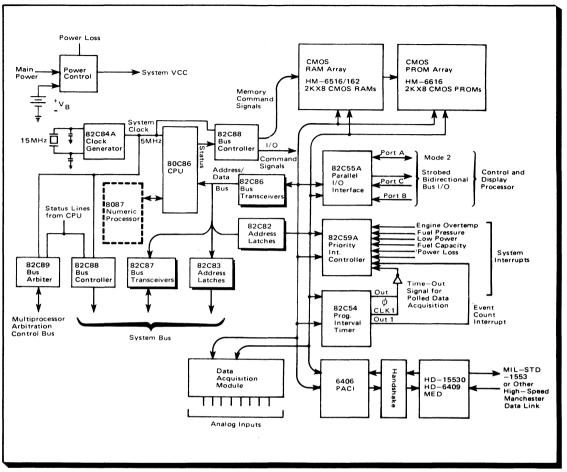

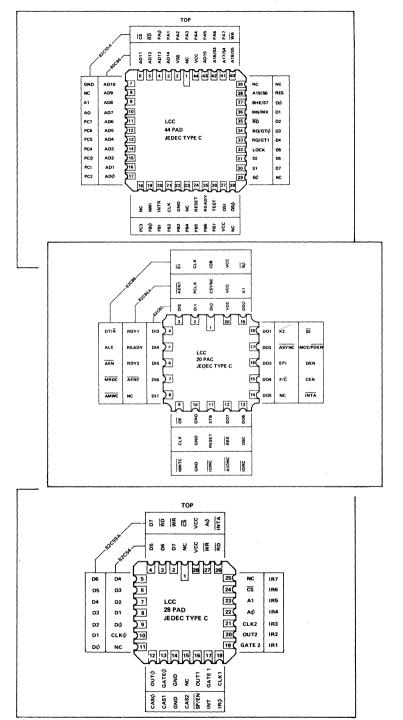

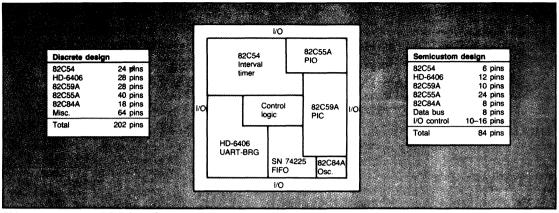

Harris is a pioneer in developing and producing digital CMOS products including: CMOS RAMs, CMOS PROMs, CMOS microprocessors, CMOS peripherals, CMOS data communications products, and a full line of 80C86/88 microprocessors and peripherals. Semicustom circuit design problems are solved by a complete line of SSI, MSI, and LSI standard cells and programmable logic products featuring on-chip testability. (See complete digital product listing, page 1-3.)

#### **CUSTOM INTEGRATED CIRCUITS DIVISION (CICD)**

CICD is dedicated to the development and production of custom/semi-custom and specialized integrated circuits for use in such areas as tactical/strategic radiation environments and secure communications. CICD employs high performance CMOS and bipolar technologies to meet the needs of high-end major military and hi-reliability programs.

CICD is oriented to engineering and manufacturing to specific customer requirements. The division also has its own dedicated manufacturing operation and engineering, product assurance, and program manager representation to insure close customer interaction and tight control of the design and quality aspects of individual programs.

Data sheet products include devices that have a wider appeal, including those designed to operate in very severe environments. CICD's experience with radiation-hardened devices has made Harris Semiconductor the leading producer of circuits that meet a variety of Department of Defense environmental specifications. (See complete CICD product listing, page 12-8 & 12-9.)

#### **MICROWAVE SEMICONDUCTOR DIVISION**

Harris Microwave Semiconductor Division develops and manufactures gallium arsenide field effect transistors (GaAs FETs), digital integrated circuits, monolithic microwave integrated circuits, and GaAs FET microwave amplifiers. (See complete Microwave product listing, page 12-8.)

Additional information on Harris products is available on VideoLog's online system. For more information check the VideoLog\* box on the reply card at the back.

Copyright (C) Harris Corporation 1986 (All rights reserved) Printed in U.S.A.

## Harris CMOS Digital Products

Harris Semiconductor continues to lead the way in offering advanced CMOS digital products for the most demanding system applications in this world — and beyond. Total control of system operation is now possible with Harris' static CMOS 80C86/88-based microprocessor and peripheral family. True low power Programmable Logic, the world's largest library of LSI Standard Cells, and advanced CMOS Memory and Memory modules are all available at Harris — just turn the pages for more on these and other advanced CMOS digital products.

This data book fully describes Harris Semiconductor's line of CMOS digital products by including a complete set of data sheets for product specifications; application notes with design details for specific applications of Harris products; and a description of Harris' quality and reliability program.

If you need more information on these and other Harris products, please contact the nearest Harris sales office listed in the back of this data book. Or return the reply card attached inside back cover.

Harris Semiconductor products are sold by description only. All specifications in this data book are applicable only to packaged products; specifications for dice are available upon request. Harris reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that data sheets and other information in this publication are current before placing orders. Information contained in the application notes is intended soley for general guidance; use of the information for user's specific application is at user's risk. Reference to products of other manufacturers are solely for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

ii

# 1986 Digital Data Book

- General Information

- CMOS Memory 2

- CMOS 80C86 Family 3

- CMOS Data Communications 4

- Digital Standard Cell Capability 5

- CMOS Harris Programmable Logic 6

- 64XX Bus Interface Circuits 7

- Article Reprints 8

10

11

12

- Harris Quality and Reliability 9

- Hi-Reliability Products

- Ordering and Packaging

## Appendices

Analog Products12-3CMOS Digital Products12-7CICD Rad Hard Products12-8CICD Future Rad Hard Products12-9Harris Microwave Semiconductor12-9Gallium Arsenide/Microwave Products12-9Harris Sales Locations12-10

# Table of Contents

| SECTION 1  | GENERAL INFORMATION                                          | PAGE         |

|------------|--------------------------------------------------------------|--------------|

|            | CMOS Alpha-Numeric Index                                     | 1-3          |

|            | CMOS Devices by Families                                     |              |

|            | Classification of Literature                                 |              |

|            | Symbols & Abbreviations                                      | 1-6          |

| SECTION 2  | CMOS MEMORY                                                  |              |

|            | CMOS Memory Product Index                                    |              |

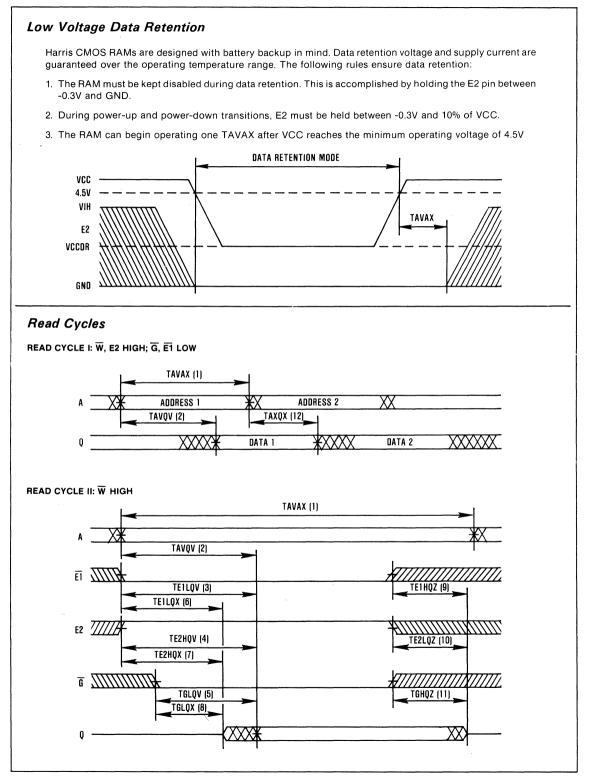

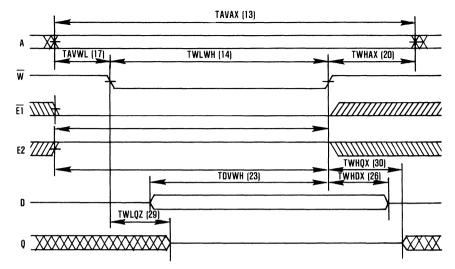

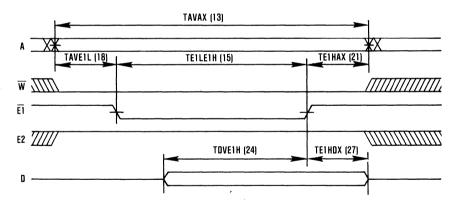

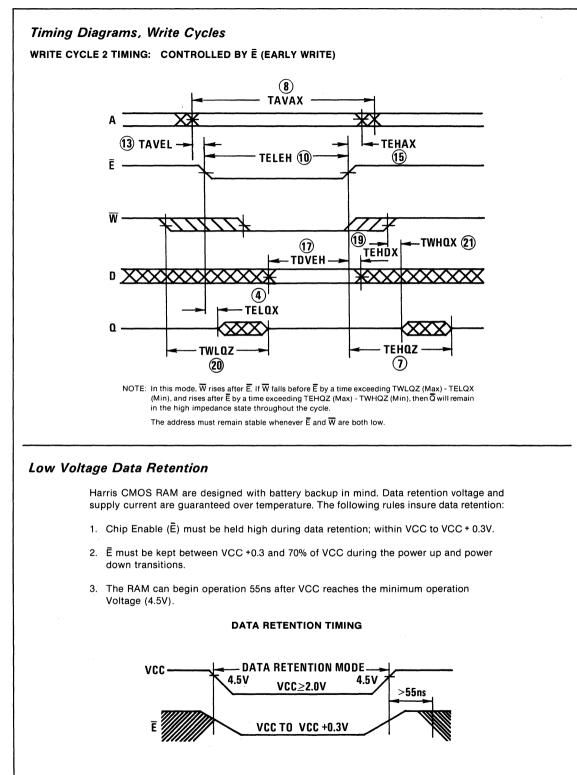

|            | Low Voltage Data Retention                                   |              |

|            | Industry CMOS RAM Cross Reference<br>1K CMOS RAM Data Sheets |              |

|            | 4K CMOS RAM Data Sheets                                      |              |

|            | 16K CMOS RAM Data Sheets                                     |              |

|            | 64K CMOS RAM Data Sheet                                      | 2-71         |

|            | CMOS RAM Module Data Sheets                                  |              |

|            | CMOS PROM Data Sheets                                        |              |

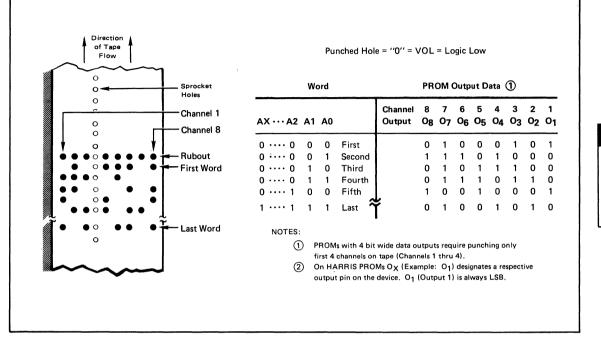

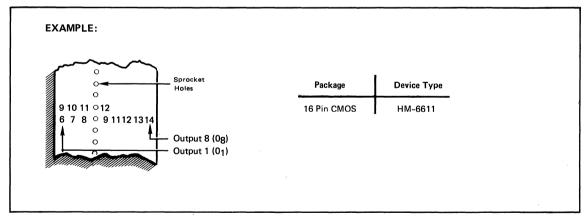

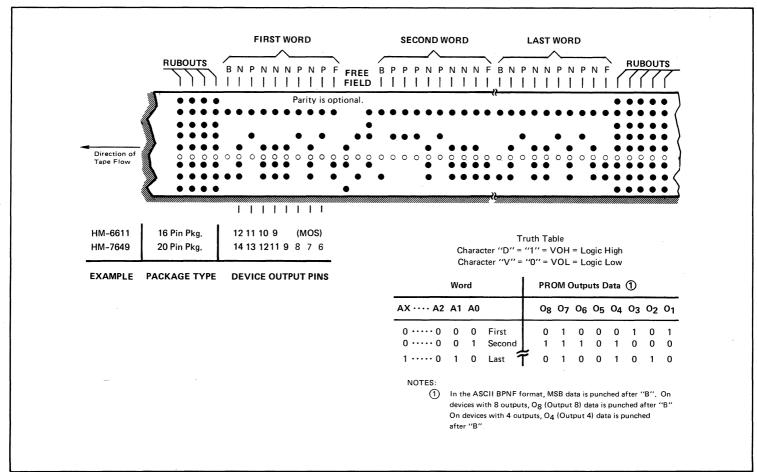

|            | Data Entry Formats for Harris Custom Programming             | 2-120        |

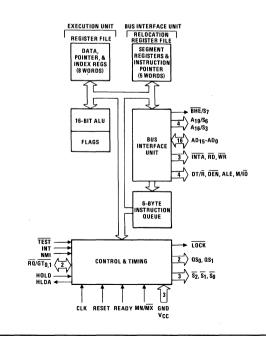

| SECTION 3  | CMOS 80C86 FAMILY                                            |              |

|            | CMOS 80C86 Family Product Index                              |              |

|            | CMOS 80C86 Family Data Sheets                                | 3-2          |

| SECTION 4  | CMOS DATA COMMUNICATIONS                                     |              |

|            | CMOS Data Communications Product Index                       |              |

|            | CMOS Data Communications Data Sheets                         | 4-3          |

| SECTION 5  | DIGITAL STANDARD CELL CAPABILITY                             |              |

|            | Digital Standard Cell Capability Index                       | 5-1          |

|            | Standard Cell Data Sheet                                     | 5-10         |

| SECTION 6  |                                                              |              |

|            | CMOS Harris Programmable Logic Product Index                 |              |

|            | CMOS Harris Programmable Logic Data Sheets                   | 6-3          |

| SECTION 7  | 64XX BUS INTERFACE CIRCUITS                                  |              |

|            | CMOS 64XX Bus Interface Product Index                        | 7-1          |

|            | CMOS Bus Driver Data Sheets                                  | 7-2          |

| SECTION 8  | ARTICLE REPRINTS                                             |              |

|            | Article Reprints Index                                       | 8-1          |

| SECTION 9  | HARRIS QUALITY AND RELIABILITY                               |              |

|            | Harris Quality and Reliability Index                         | 9-1          |

| SECTION 10 | HI-RELIABILITY PRODUCTS                                      |              |

| SECTION TO |                                                              | 10.1         |

|            | Hi-Reliability Products Index                                | 10-1         |

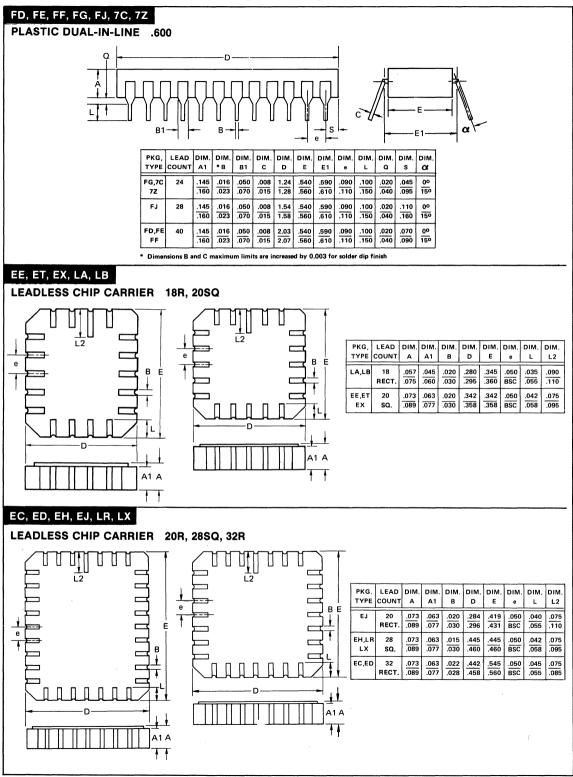

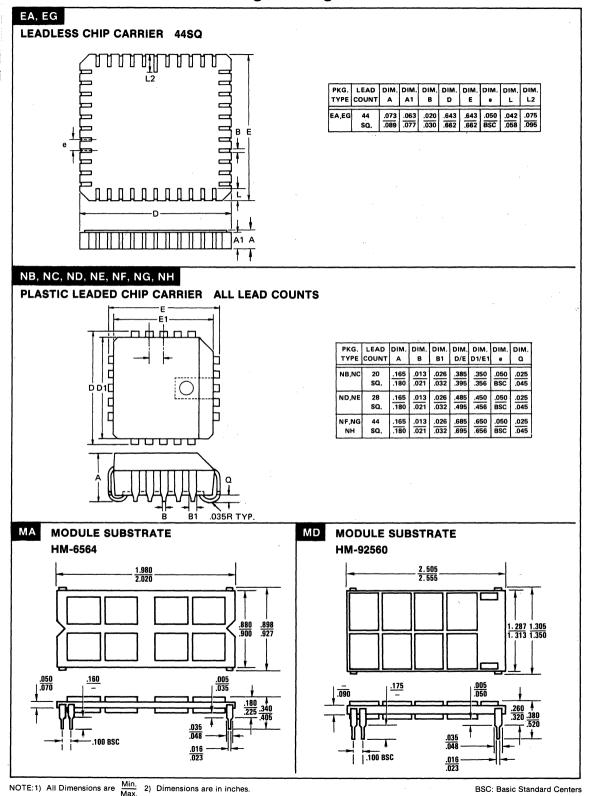

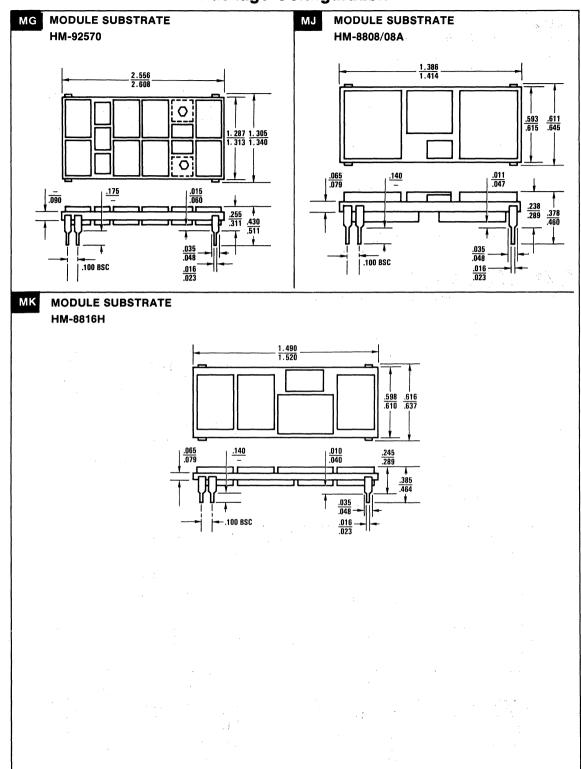

| SECTION 11 | ORDERING AND PACKAGING                                       |              |

|            | Ordering and Packaging Index                                 | 11-1         |

|            | Dice Information                                             | 11-3         |

| SECTION 12 | APPENDICES                                                   |              |

|            | Analog Products                                              | 12-3         |

|            | CMOS Digital Products                                        | 12-7<br>12-8 |

|            | CICD Future Rad Hard Products                                |              |

|            | Harris Microwave/Gallium Arsenide Microwave Products         |              |

|            | Harris Sales Locations                                       |              |

# General Information

#### PAGE

| CMOS ALPHA-NUMERIC INDEX | 1-3 |

|--------------------------|-----|

| CMOS DEVICES BY FAMILIES | 1-4 |

|                          | 1-6 |

| SYMBOLS & ABBREVIATIONS  | 1-6 |

.

## **CMOS Alpha-Numeric Index**

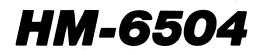

#### DESCRIPTION PRODUCT PAGE HD-15530 Manchester Encoder-Decoder 4-40 HD-15531 Manchester Encoder-Decoder 4-47 HD-4702 HD-6402 Universal Asynchronous Receiver Transmitter...... 4-8 Programmable Asynchronous Communication Interface ...... 4-14 HD-6406 Asynchronous Serial Manchester Adapter ..... 4-25 HD-6408 Manchester Encoder-Decoder 4-30 HD-6409 HD-6431 HD-6432 HD-6433 HD-6434 HD-6436 HD-6440 HD-6495 HM-6504 4K x 1 Synchronous RAM ..... 2-28 HM-6508 1K x 1 Synchronous RAM ..... 2-4 HM-6514 1K x 4 Synchronous RAM ...... 2-39 HM-6516 HM-65162 2K x 8 Asynchronous RAM ..... 2-55 HM-6518 1K x 1 Synchronous RAM ...... 2-10 HM-65262 16K x 1 Asynchronous RAM ...... 2-62 HM-6551 256 x 4 Synchronous RAM...... 2-16 256 x 4 Synchronous RAM...... 2-22 HM-6561 64K Synchronous RAM Module ..... 2-76 HM-6564 8K x 8 Asynchronous RAM ...... 2-71 HM-65642 HM-6616 HM-6641 HM-8808/08A 8K x 8 Asynchronous RAM Modules ..... 2-85 HM-8816H 16K x 8/32K x 8 Asynchronous RAM Module...... 2-94 HM-92560 256K Buffered Synchronous RAM Module ...... 2-106 HM-92570 HPL<sup>™</sup>-16LC8 HPL-16RC8/6/4 HPL-82C138 HPL-82C139 Programmable Chip Select Decoder (PCSD) ...... 6-30 HPL-82C338 HPL-82C339 Mini-HPL™ 80C86 80C88 Static 8/16-Bit Microprocessor ...... 3-25 82C37A 82C50A 82C52 82C54 82C55A 82C59A 82C82 82C83H 82C84A 82C85 82C86H/87H 82C88 82C89

PCSD™, HPL™, Mini-HPL™ are trademarks of Harris Corporation

GENERAL Information

1

## **CMOS Devices by Families**

| 8/16-BIT MICROPROCESSOR |                                              |       |  |  |

|-------------------------|----------------------------------------------|-------|--|--|

| 80C86                   | Static 16-Bit Microprocessor                 | 3-2   |  |  |

| 80C88                   | Static 8/16-Bit Microprocessor               | 3-25  |  |  |

| 80C86/88 PERIPH         |                                              |       |  |  |

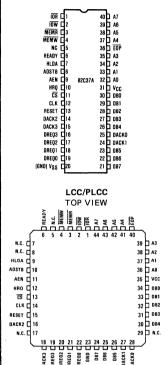

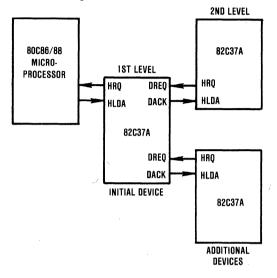

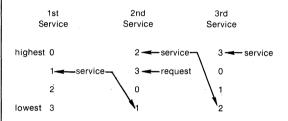

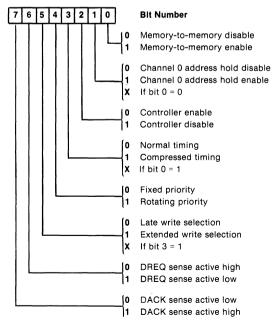

| 82C37A                  | High Performance Programmable DMA Controller | 3-50  |  |  |

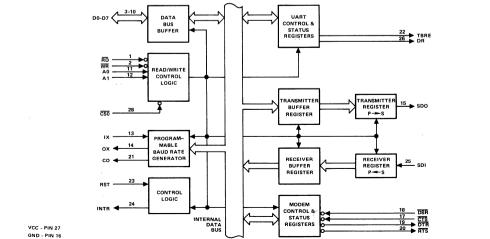

| 82C50A                  | Asynchronous Communications Element          | 3-68  |  |  |

| 82C52                   | Serial Controller Interface                  | 3-88  |  |  |

| 82C54                   | Programmable Interval Timer                  | 3-98  |  |  |

| 82C55A                  | Programmable Peripheral Interface            | 3-113 |  |  |

| 82C59A                  | Priority Interrupt Controller                | 3-133 |  |  |

| App Note 109            | 82C59A Priority Interrupt Controller         | 3-203 |  |  |

#### 80C86/88 BUS SUPPORT CIRCUITS

| 82C82      | Octal Latching Bus Driver           | 3-147 |

|------------|-------------------------------------|-------|

| 82C83H     | Octal Latching Inverting Bus Driver | 3-152 |

| 82C84A     | Clock Generator Driver              | 3-157 |

| 82C85      | Static Clock Controller/Generator   |       |

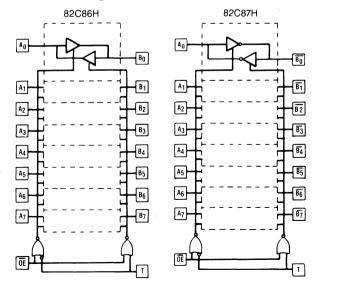

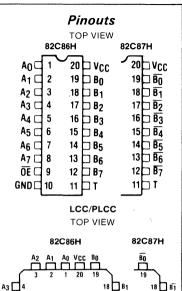

| 82C86H/87H | Octal Bus Transceivers              | 3-181 |

| 82C88      | Bus Controller                      | 3-186 |

| 82C89      | Bus Arbiter                         | 3-193 |

#### 64XX BUS INTERFACE CIRCUITS

| HD-6431 | Hex Latching Bus Driver       | 7-2 |

|---------|-------------------------------|-----|

| HD-6432 | Hex Bi-Directional Bus Driver | 7-3 |

| HD-6433 | Quad Bus Separator/Driver     | 7-4 |

| HD-6434 | Octal Resettable Latch        | 7-5 |

| HD-6436 | Octal Bus Buffer/Driver       | 7-6 |

| HD-6440 | Latch Decoder/Driver          | 7-7 |

| HD-6495 | Hex Bus Driver                | 7-8 |

#### SERIAL COMMUNICATIONS CIRCUITS

| HD-4702      | Programmable Bit Rate Generator                   | 4-3  |

|--------------|---------------------------------------------------|------|

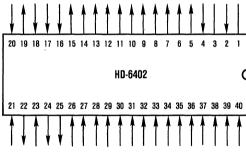

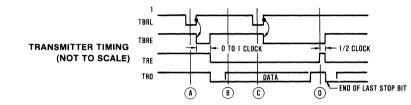

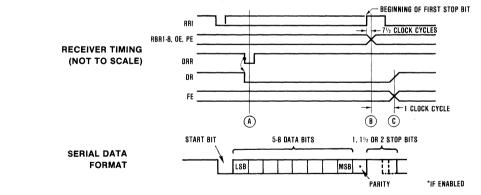

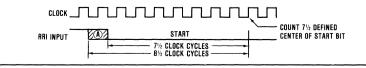

| HD-6402      | Universal Asynchronous Receiver Transmitter       | 4-8  |

| HD-6406      | Programmable Asynchronous Communication Interface | 4-14 |

| HD-6408      | Asynchronous Serial Manchester Adapter            | 4-25 |

| HD-6409      | Manchester Encoder-Decoder                        | 4-30 |

| HD-15530     | Manchester Encoder-Decoder                        | 4-40 |

| HD-15531     | Manchester Encoder-Decoder                        | 4-47 |

| App Note 108 | HD-6406 Software Applications Adapter             | 4-56 |

# CMOS Devices by Families

|                |                                         | PAGE  |

|----------------|-----------------------------------------|-------|

| CMOS STATIC RA |                                         |       |

| HM-6508        | 1K x 1 Synchronous RAM                  | 2-4   |

| HM-6518        | 1K x 1 Synchronous RAM                  |       |

| HM-6551        | 256 x 4 Synchronous RAM                 |       |

| HM-6561        | 256 x 4 Synchronous RAM                 | 2-22  |

| 4K — SYNCHRON  | OUS                                     |       |

| HM-6504        | 4K x 1 Synchronous RAM                  | 2-28  |

| HM-6514        | 1K x 4 Synchronous RAM                  | 2-39  |

| 16K - SYNCHRO  |                                         |       |

| HM-6516        | 2K x 8 Synchronous RAM                  | 2-50  |

| 16K - ASYNCHRO | ONOUS                                   |       |

| HM-65162       | 2K x 8 Asynchronous RAM                 | 2-55  |

| HM-65262       | 16K x 1 Asynchronous RAM                | 2-62  |

| 64K - ASYNCHRO | ONOUS                                   |       |

| HM-65642       | 8K x 8 Asynchronous RAM                 | 2-71  |

| CMOS RAM MOD   | ULE                                     |       |

| HM-6564        | 64K Synchronous RAM Module              | 2-76  |

| HM-8808/08A    | 8K x 8 Asynchronous RAM Modules         | 2-85  |

| HM-8816H       | 16K x 8/32K x 8 Asynchronous RAM Module | 2-94  |

| HM-92560       | 256K Synchronous RAM Module             | 2-99  |

| HM-92570       | 256K Buffered Synchronous RAM Module    | 2-106 |

| CMOS FUSE LINK | PROMS                                   |       |

| HM-6641        | 512 x 8 Fuse Link PROM                  | 2-113 |

| HM-6616        | 2K x 8 Fuse Link PROM                   | 2-118 |

| CMOS PROGRAM   |                                         |       |

| HPL-16LC8      | Programmable Logic                      | 6-3   |

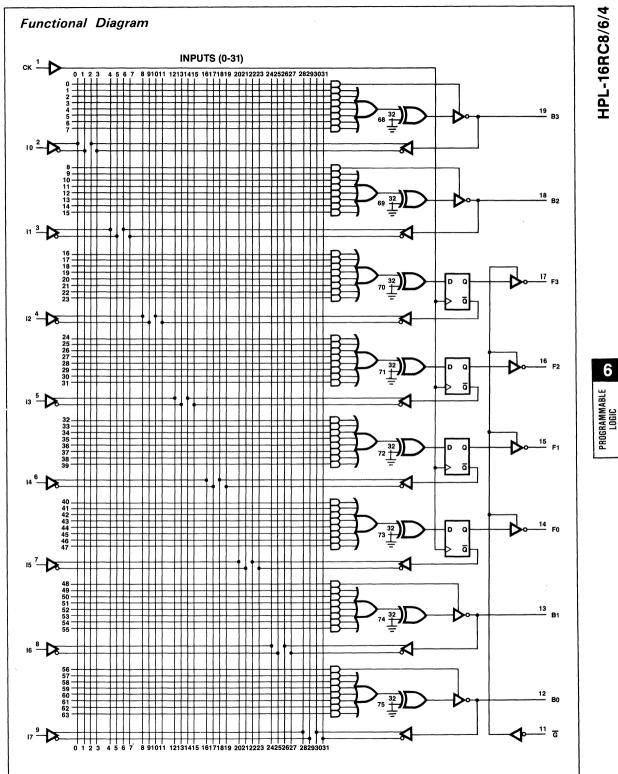

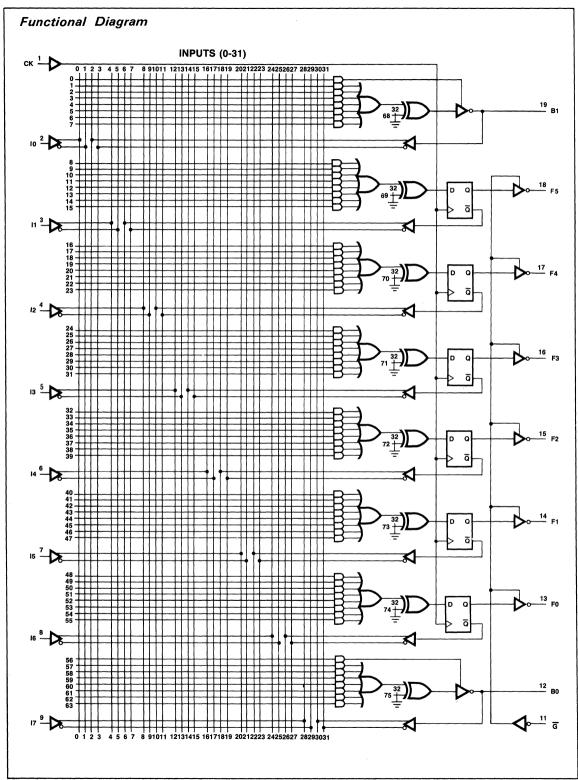

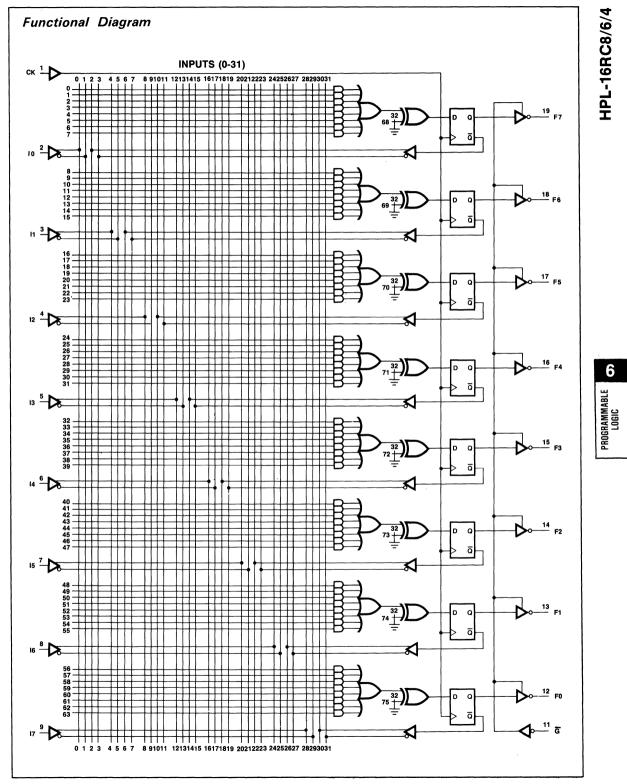

| HPL-16RC8/6/4  |                                         |       |

| HPL-82C339     | Programmable Chip Select Decoder (PCSD) | 6-20  |

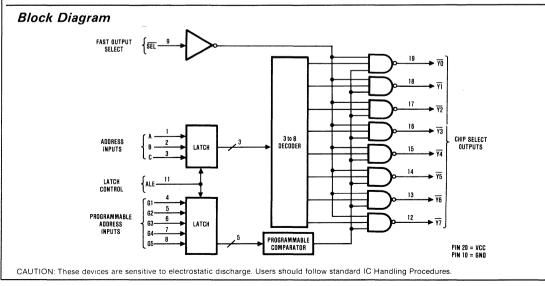

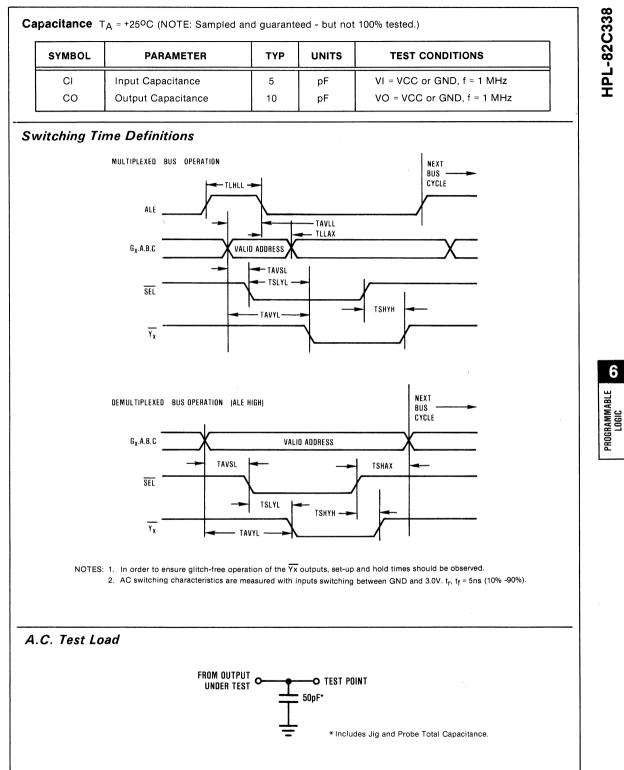

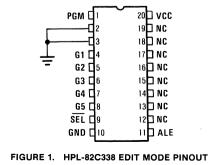

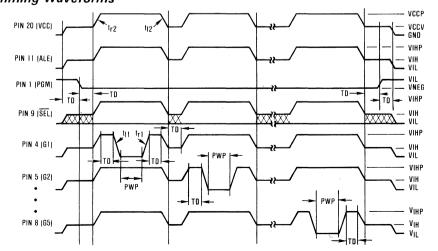

| HPL-82C338     | Programmable Chip Select Decoder (PCSD) | 6-25  |

| HPL-82C139     | Programmable Chip Select Decoder (PCSD) | 6-30  |

| HPL-82C138     | Programmable Chip Select Decoder (PCSD) | 6-35  |

| Mini-HPL       | Programmable Logic (16-Pin)             | 6-40  |

1

1-5

| CLASSIFICATION                                   | PRODUCT STAGE                 | DISCLAIMERS                                                                                                                                 |  |  |  |

|--------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <b>Preview</b> Formative or Design<br>DATA SHEET |                               | This document contains the design specifications for product under development<br>Specifications may be changed in armanner without notice. |  |  |  |

| Advance Information                              | Sampling or<br>Pre-Production | This is advanced information, and specifica-<br>tions are subject to change without notice.                                                 |  |  |  |

## **Classification of Literature**

Harris reserves the right to make changes at anytime without notice, in order to improve design and supply the best product possible.

## **Symbols and Abbreviations**

This data sheet utilizes a new set of specification nomenclature. This new format is an IEEE and JEDEC supported standard for semiconductor memories. It is intended to clarify the symbols, abbreviations and definitions, and to make all memory data sheets consistent. We believe that, once acclimated, you will find this standardized format easy to read and use.

#### **Electrical Parameter Abbreviations**

All abbreviations use upper case letters with no subscripts. The initial symbol is one of these four characters:

- V (Voltage)

- I (Current)

- P (Power)

- C (Capacitance)

The second letter specifies input (I) or output (O), and the third letter indicates the high (H), low (L) or off (Z) state of the pin during measurements. Examples:

VIL - Input Low Voltage

IQZ — Output Leakage Current

#### **Timing Parameter Abbreviations**

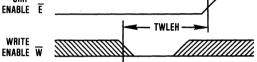

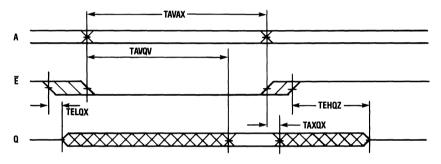

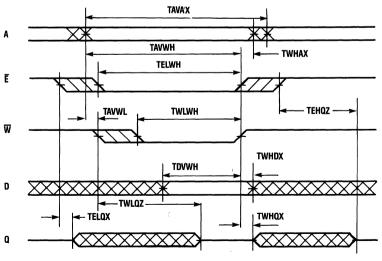

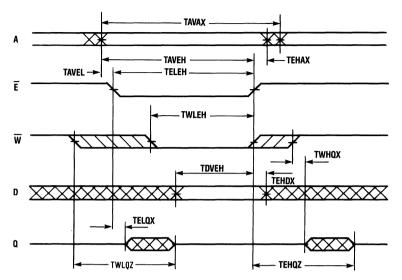

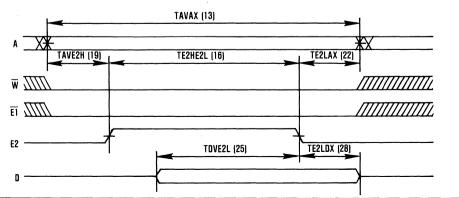

All timing abbreviations use upper case characters with no subscripts. The initial character is always T and is followed by four descriptors. These characters specify two signal points arranged in a "from-to" sequence that define a timing interval. The two descriptors for each signal point specify the signal name and the signal transitions. Thus the format is: T X X X X

Signal name from which interval is defined \_\_\_\_\_\_ Transition direction for first signal \_\_\_\_\_\_ Signal name to which interval is defined \_\_\_\_\_\_ Transition direction for second signal \_\_\_\_\_\_

#### Signal Definitions:

- A = Address

- D = Data In

- Q = Data Out

- W = Write Enable

- E = Chip Enable

- S = Chip Select

- G = Output Enable

#### Transition Definitions:

- H = Transition to High

- L = Transition to Low

- V = Transition to Valid

- X = Transition to Invalid or Don't Care

- Z = Transition to Off (High Impedance)

The example shows Write pulse setup time defined as TWLEH-Time from Write enable Low to chip Enable High.

#### **Timing Limits**

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address set-up time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

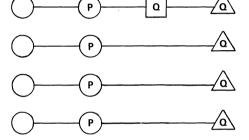

#### Waveforms

| WAVEFORM<br>SYMBOL | INPUT                                  | OUTPUT                        |

|--------------------|----------------------------------------|-------------------------------|

|                    | Must Be<br>Valid                       | Will be<br>Valid              |

|                    | Change<br>From H to L                  | Will Change<br>From H to L    |

|                    | Change<br>From L to H                  | Will Change<br>From L to H    |

|                    | Don't Care:<br>Any Change<br>Permitted | Changing:<br>State<br>Unknown |

| $\rightarrow$      |                                        | High<br>Impedance             |

|                    |                                        |                               |

-

# **CMOS Memory**

#### PAGE

| LOW VOLTAGE DATA RETENTION        |                                      |       |  |  |  |

|-----------------------------------|--------------------------------------|-------|--|--|--|

| INDUSTRY CMOS RAM CROSS REFERENCE |                                      |       |  |  |  |

| 1K CMOS RAM                       | DATA SHEETS                          |       |  |  |  |

| HM-6508                           | 1K x 1 Synchronous RAM               | 2-4   |  |  |  |

| HM-6518                           | 1K x 1 Synchronous RAM               | 2-10  |  |  |  |

| HM-6551                           | 256 x 4 Synchronous RAM              | 2-16  |  |  |  |

| HM-6561                           | 256 x 4 Synchronous RAM              | 2-22  |  |  |  |

| 4K CMOS RAM                       | DATA SHEETS                          |       |  |  |  |

| HM-6504                           | 4K x 1 Synchronous RAM               | 2-28  |  |  |  |

| HM-6514                           | 1K x 4 Synchronous RAM               | 2-39  |  |  |  |

| 16K CMOS RAM                      | DATA SHEETS                          |       |  |  |  |

| HM-6516                           | 2K x 8 Synchronous RAM               | 2-50  |  |  |  |

| HM-65162                          | 2K x 8 Asynchronous RAM              | 2-55  |  |  |  |

| HM-65262                          | 16K x 1 Asynchronous RAM             | 2-62  |  |  |  |

| 64K CMOS RAM                      |                                      |       |  |  |  |

| HM-65642                          | 8K x 8 Asynchronous RAM              | 2-71  |  |  |  |

| CMOS RAM MO                       | DULE DATA SHEETS                     |       |  |  |  |

| HM-6564                           | 64K Synchronous RAM Module           | 2-76  |  |  |  |

| HM-8808/08A                       | 8K x 8 Asynchronous RAM Modules      | 2-85  |  |  |  |

| HM-8816H                          | 16K x 8 Asynchronous RAM Module      | 2-94  |  |  |  |

| HM-92560                          | 256K Synchronous RAM Module          | 2-99  |  |  |  |

| HM-92570                          | 256K Synchronous RAM Module          | 2-106 |  |  |  |

| CMOS PROM DA                      | ATA SHEETS                           |       |  |  |  |

| HM-6641                           | 512 x 8 Fuse Link PROM               | 2-113 |  |  |  |

| HM-6616                           | 2K x 8 Fuse Link PROM                | 2-118 |  |  |  |

| DATA ENTRY F                      | ORMATS FOR HARRIS CUSTOM PROGRAMMING | 2-126 |  |  |  |

2

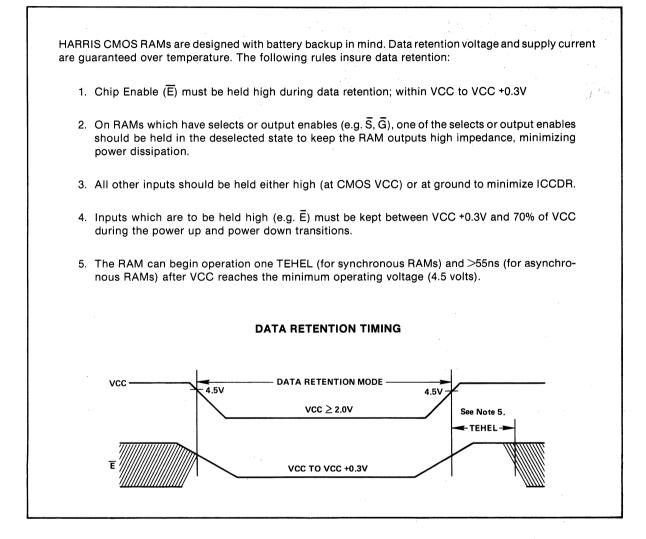

## Low Voltage Data Retention

## Industry CMOS RAM Cross Reference

#### HARRIS CMOS RAMs

| DESCRIPTION                                   | HARRIS                            | AMD            | EDI           | FUJ-<br>ITSU | HIT-<br>ACHI | IDT                    | MITSU-<br>BISHI | MOT-<br>OROLA | NAT-<br>IONAL  | NEC  | окі          | RCA          | SMOS         | TOSH-<br>IBA | NMOS,<br>OTHER                   |

|-----------------------------------------------|-----------------------------------|----------------|---------------|--------------|--------------|------------------------|-----------------|---------------|----------------|------|--------------|--------------|--------------|--------------|----------------------------------|

| 1K CMOS RAMs                                  |                                   |                |               |              | -            |                        |                 |               |                |      |              |              |              |              |                                  |

| 1Kx1, 16 Pin<br>Synchronous                   | HM-6508                           |                |               | 8401         |              |                        |                 | 6508          | 6508<br>74C929 | 443  |              | 6508<br>1821 |              | 5508         | 2125, 4015                       |

| 1Kx1, 18 Pin<br>Synchronous                   | HM-6518                           |                |               |              |              |                        |                 | 6518          | 6518<br>74C930 |      |              |              |              |              |                                  |

| 256x4, 22 Pin<br>Synchronous                  | HM-6551                           |                |               |              |              |                        |                 |               | 6551<br>74C920 |      |              | 1822<br>5101 |              | 5101         | 2101                             |

| 256x4, 18 Pin<br>Synchronous                  | HM-6561                           |                |               |              |              |                        |                 |               |                |      |              |              |              |              | 2111                             |

| 4K CMOS RAMs                                  |                                   |                |               |              |              |                        |                 |               |                |      |              |              |              |              |                                  |

| 4Kx1, 18 Pin<br>Synchronous                   | HM-6504                           | 92L44          |               | 8404         | 4315<br>6147 |                        |                 | 6504          | 6504           |      | 5104         |              | 6504         | 5504         | 2141, 2147<br>315D, 4104<br>4404 |

| 1Kx4, 18 Pin<br>Synchronous                   | HM-6514                           | 91L14<br>91L24 |               | 8414         | 4334<br>6148 |                        | 58981           | 6514          | 6514           | 444  | 5114<br>5115 | 5114         | 6514         | 5514         | 2114, 2148<br>2149, 4045<br>314A |

| 16K CMOS RAM                                  | 8                                 |                |               |              |              |                        |                 |               |                |      |              |              |              |              |                                  |

| 2Kx8, 24 Pin<br>Synchronous                   | HM-6516                           |                |               |              |              |                        |                 |               | 6516           |      |              |              |              |              |                                  |

| 2Kx8, 24 Pin<br>Asynchronous                  | HM-65162                          |                |               | 8416         | 6116         | 6116                   | 5117            | 65116         | 6116           | 446  | 5128         | 6116         | 2016         | 5517         | 4802, 2116<br>2016, 4016         |

| 16Kx1, 20 Pin<br>Asynchronous                 | HM-65262                          |                |               | 8167         | 6167         | 6167                   |                 |               |                |      |              |              | 2267<br>2367 |              | 2167, 8167<br>1400               |

| 64K CMOS RAM                                  | S                                 |                |               |              |              |                        |                 |               |                |      |              |              |              |              |                                  |

| 8Kx8, 28 Pin<br>Asynchronous                  | HM-65642<br>HM-8808A*<br>HM-8808* | 99C88          | 8808A<br>8808 | 8464         | 6264         | 7164<br>7M864<br>8M864 | 5164            | 6164          | 6164           | 4464 |              | 6264         | 2064<br>2264 | 5564<br>5565 |                                  |

| 128K CMOS RAM MODULE                          |                                   |                |               |              |              |                        |                 |               |                |      |              |              |              |              |                                  |

| 16Kx8, 28 Pin<br>Asynchronous                 | HM-8816H                          |                | 8816H         |              |              |                        |                 |               |                |      |              |              |              |              |                                  |

| 256K CMOS RAM                                 | 256K CMOS RAM MODULE              |                |               |              |              |                        |                 |               |                |      |              |              |              |              |                                  |

| 32Kx8/16Kx16<br>48 Pin Module<br>Asynchronous | HM-92560<br>HM-92570              |                |               |              |              |                        |                 |               |                |      |              |              |              |              |                                  |

2-3

CMOS Memory

N

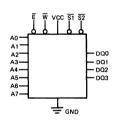

# HM-6508

### 1024 x 1 CMOS RAM

16 VCC

15]]D 14]]₩

13 1 49

12 A8

11 A7

10 A6

9 T A5

D – Data Input

Q - Data Output

Pinout

TOP VIEW

E 🗌

A0 🗖

A1 🛛 3

A2 🗌

A – Address Input

E - Chip Enable

W - Write Enable

6

Logic Symbol

E +VCC W

≟ GND

#### Features

| Low Standby Power                                   | 50µW Max.      |

|-----------------------------------------------------|----------------|

| Low Operating Power                                 | 20mW/MHz Max.  |

| Fast Access Time                                    | 180nsec Max.   |

| Data Retention Voltage                              | 2.0 Volts Min. |

| TTL Compatible In/Out                               |                |

| <ul> <li>High Output Drive — 2 TTL Loads</li> </ul> |                |

| High Noise Immunity                                 |                |

| On Chip Address Register                            |                |

| Wide Operating Temperature Ranges:                  |                |

| ► HM-6508-5                                         | 0°C to +70°C   |

| ► HM-6508-9                                         |                |

#### Description

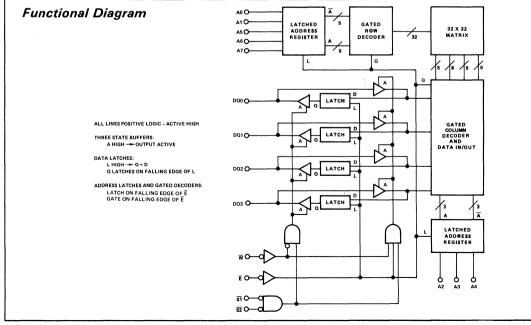

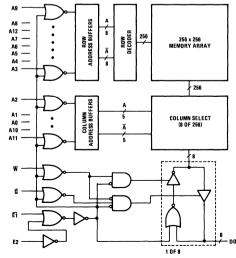

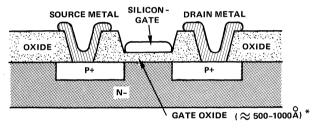

The HM-6508 is a 1024 by 1 static CMOS RAM fabricated using selfaligned silicon gate technology. Synchronous circuit design techniques are employed to achieve high performance and low power operation.

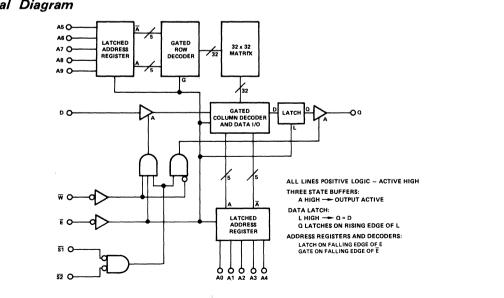

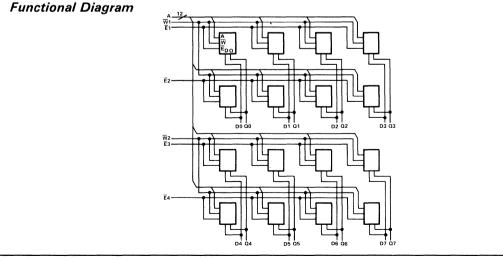

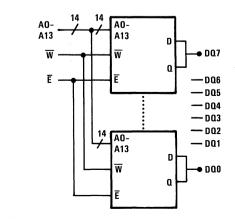

On chip latches are provided for address allowing efficient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays.

The HM-6508 is a fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are guaranteed over temperature.

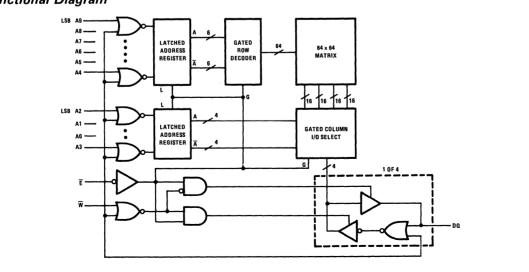

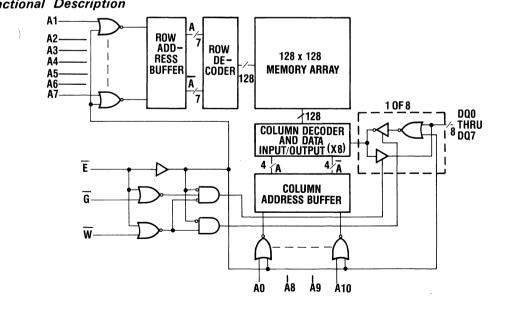

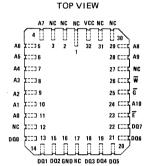

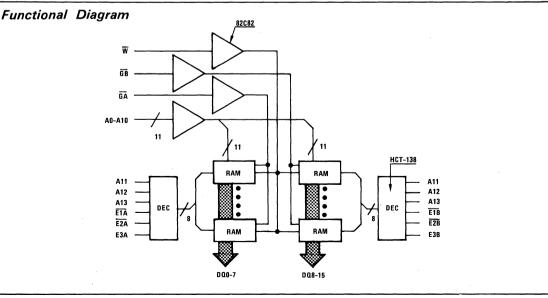

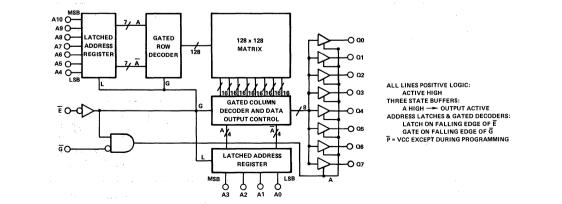

#### Functional Diagram

| Supply Voltage - (VCC - GND)    | 0.3V to +8.0V  |

|---------------------------------|----------------|

| Input or Output Voltage Applied | (GND -0.3V)    |

|                                 | to (VCC +0.3V) |

| Storage Temperature             | 65°C to +150°C |

#### **Operating Range**

| Operating Supply Voltage - VCC | - 1            |

|--------------------------------|----------------|

| HM-6508B-2/-8                  | 4.5V to 5.5V   |

| HM-6508B-9                     | 4.5V to 5.5V   |

| Operating Temperature          |                |

| HM-6508B-2/-8                  | 55°C to +125°C |

| HM-6508B-9                     | 40°C to +85°C  |

\*CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electrical Specifications** ①

|      |                |                                                                     | TEMP. 8<br>OPERA<br>RAN | TING       |          | TEST                                    |

|------|----------------|---------------------------------------------------------------------|-------------------------|------------|----------|-----------------------------------------|

|      | SYMBOL         | PARAMETER                                                           | MIN                     | MAX        | UNITS    | CONDITIONS                              |

|      | ICCSB          | Standby Supply Current                                              |                         | 10         | μΑ       | IO = 0<br>VI = VCC or GND               |

|      | ICCOP          | Operating Supply Current ②                                          |                         | 4          | mA       | Ē = 1MHz, IO = 0<br>VI = VCC or GND     |

|      | ICCDR          | Data Retention Supply Current                                       |                         | 5          | μΑ       | VCC = 2.0, IO = 0<br>VI = VCC or GND    |

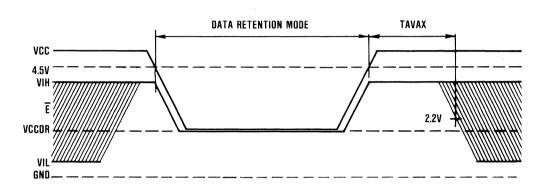

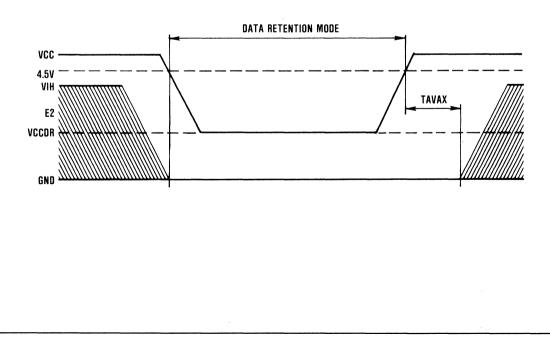

|      | VCCDR          | Data Retention Supply Voltage                                       | 2.0                     |            | v        | Ē = VCC                                 |

| D.C. | 11             | Input Leakage Current                                               | -1.0                    | +1.0       | μΑ       | VI = VCC or GND                         |

| D.C. | IOZ            | Output Leakage Current                                              | -1.0                    | +1.0       | μΑ       | VO = VCC or GND                         |

|      | VIL            | Input Low Voltage                                                   | -0.3                    | 0.8        | v        |                                         |

| 1    | VIH            | Input High Voltage                                                  | VCC -2.0                | VCC +0.3   | v        |                                         |

|      | VOL            | Output Low Voltage                                                  |                         | 0.4        | v        | 10 = 3.2mA                              |

|      | voн            | Output High Voltage                                                 | 2.4                     |            | v        | IO = -0.4mA                             |

|      | CI             | Input Capacitance ③                                                 |                         | 6          | pF       | VI = VCC or GND                         |

|      | со             | Output Capacitance ③                                                |                         | 10         | pF       | f = 1MHz<br>VO = VCC'or GND<br>f = 1MHz |

| ł    |                |                                                                     |                         |            | r        |                                         |

|      | TELQV          | Chip Enable Access Time                                             |                         | 180        | ns       | (4)<br>(4)                              |

|      | TAVQV          | Address Access Time                                                 |                         | 180        | ns       | (4)                                     |

|      | TELQX          | Chip Enable Output Enable Time                                      | 20                      | 120        | ns       | 34                                      |

|      | TWLQZ<br>TEHQZ | Write Enable Output Disable Time                                    |                         | 120<br>120 | ns       |                                         |

|      | TELEH          | Chip Enable Output Disable Time<br>Chip Enable Pulse Negative Width | 180                     | 120        | ns       |                                         |

|      | TEHEL          | Chip Enable Pulse Positive Width                                    | 100                     |            | ns<br>ns |                                         |

| A.C. | TAVEL          | Address Setup Time                                                  | 0                       |            | ns       | a l                                     |

|      | TELAX          | Address Hold Time                                                   | 40                      |            | ns       | - <b>(</b>                              |

|      | TDVWH          | Data Setup Time                                                     | 80                      |            | ns       | Ă                                       |

|      | TWHDX          | Data Hold Time                                                      | 0                       |            | ns       | ă                                       |

|      | TWLEH          | Chip Enable Write Pulse Setup Time                                  | 100                     |            | ns       | <b>()</b>                               |

| -    | TELWH          | Chip Enable Write Pulse Hold Time                                   | 100                     |            | ns       | Ā                                       |

|      | TWLWH          | Write Enable Pulse Width                                            | 100                     |            | ns       | 4                                       |

|      | TELEL          | Read or Write Cycle Time                                            | 280                     |            | ns       | . 4                                     |

NOTES: ① All devices tested at worst case temperature and V<sub>CC</sub>.

Operating supply current (ICCOP) is proportional to operating frequency. Example: typical ICCOP = 1.5mA/MHz.

Tested at initial design and after major design changes.

Input rise and fall times: 20ns max. Input and output timing reference level: 1.5V. Output load: 1 TTL gate equivalent and C<sub>L</sub> = 50 to 300pF. For C<sub>L</sub> greater than 50pF, access time is derated 0.15ns/pF. HM-6508

| Absolute Maximum Rati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ngs*                     | Operating Range                |                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------|-----------------|

| Supply Voltage - (VCC - GNE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | )0.3V to +8.0V           | Operating Supply Voltage - VCC |                 |

| Input or Output Voltage Appl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | HM-6508-2/-8                   | 4.5V to 5.5V    |

| A second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          | HM-6508-9                      | 4.5V to 5.5V    |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65°C to +150°C           | Operating Temperature          |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18 - E - 1 <sup>87</sup> | HM-6508-2/-8                   | -55°C to +125°C |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                        | HM-6508-9                      | 40°C to +85°C   |

| <ul> <li>A second sec<br/>second second sec</li></ul> |                          |                                |                 |

\*CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electrical Specifications** ①

ſ

|      |        |                                    | TEMP. 8<br>OPERA<br>RAN |          |       | TEST                                 |

|------|--------|------------------------------------|-------------------------|----------|-------|--------------------------------------|

|      | SYMBOL | PARAMETER                          | MIN                     | МАХ      | UNITS | CONDITIONS                           |

|      | ICCSB  | Standby Supply Current             |                         | 10       | μΑ    | 10 = 0<br>V1 = VCC or GND            |

|      | ICCOP  | Operating Supply Current ②         |                         | 4        | mA    | Ē = 1MHz, IO = 0<br>VI = VCC or GND  |

|      | ICCDR  | Data Retention Supply Current      |                         | 10       | μΑ    | VCC = 2.0, IO = 0<br>VI = VCC or GND |

|      | VCCDR  | Data Retention Supply Voltage      | 2.0                     |          | v     | Ē = VCC                              |

|      | н      | Input Leakage Current              | -1.0                    | +1.0     | UA    | VI = VCC or GND                      |

| D.C. | IOZ    | Output Leakage Current             | -1.0                    | +1.0     | μΑ    | VO = VCC or GND                      |

|      | VIL    | Input Low Voltage                  | -0.3                    | 0.8      | v     |                                      |

|      | VIH    | Input High Voltage                 | VCC -2.0                | VCC +0.3 | v     |                                      |

|      | VOL    | Output Low Voltage                 |                         | 0.4      | v     | IO = 3.2mA                           |

|      | VOH    | Output High Voltage                | 2.4                     |          | V     | 10 = -0.4mA                          |

|      | СІ     | Input Capacitance ③                |                         | 6        | pF    | VI = VCC or GND                      |

|      |        |                                    |                         |          |       | f = 1MHz                             |

|      | со     | Output Capacitance ③               |                         | 10       | pF    | VO=VCC or GND<br>f = 1MHz            |

|      | TELOV  | Chip Enable Access Time            | т.<br>Т. с.             | 250      | ns    | A                                    |

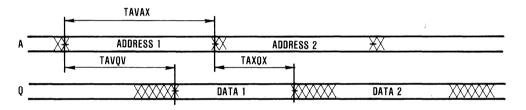

|      | TAVQV  | Address Access Time                | 4                       | 250      | ns    | (4)<br>(4)                           |

|      | TELQX  | Chip Enable Output Enable Time     | 20                      | 160      | ns    | <u>3</u> 4                           |

|      | TWLQZ  | Write Enable Output Disable Time   |                         | 160      | ns    | 34                                   |

|      | TEHQZ  | Chip Enable Output Disable Time    |                         | 160      | ns    | <u>3</u> 4                           |

|      | TELEH  | Chip Enable Pulse Negative Width   | 250                     | × +      | ns    | <u>(4)</u>                           |

| A.C. | TEHEL  | Chip Enable Pulse Positive Width   | 100                     |          | ns    | ā a                                  |

|      | TAVEL  | Address Setup Time                 | Ö                       | ,<br>,   | ns    | 4                                    |

|      | TELAX  | Address Hold Time                  | 50                      |          | ns    |                                      |

|      | TDVWH  | Data Setup Time                    | 110                     |          | ns    |                                      |

|      | TWHDX  | Data Hold Time                     | 0                       |          | ns    | (4)                                  |

|      | TWLEH  | Chip Enable Write Pulse Setup Time | 130                     |          | nş    | (4)                                  |

|      | TELWH  | Chip Enable Write Pulse Hold Time  | 130                     | 12 - A   | ns    | (4)                                  |

|      | TWLWH  | Write Enable Pulse Width           | 130                     |          | ns    | @ @ @ @ @ @ @                        |

|      | TELEL  | Read or Write Cycle Time           | 350                     |          | ns    | (4)                                  |

NOTES: (1) All devices tested at worst case temperature and V<sub>CC</sub>.

② Operating supply current (ICCOP) is proportional to operating frequency. Example: typical ICCOP = 1.5mA/MHz.

③ Tested at initial design and after major design changes.

(e) Input rise and fall times: 20ns max. Input and output timing reference level: 1.5V. Output load: 1 TTL gate equivalent and C<sub>L</sub> = 50 to 300pF. For C<sub>L</sub> greater than 50pF, access time is derated 0.15ns/pF.

#### **Operating Range**

| Supply Voltage - (VCC - GND)0.3V to +8.0V   | Operating Supply Voltage - VCC |

|---------------------------------------------|--------------------------------|

| Input or Output Voltage Applied (GND -0.3V) | HM-6508-5 4.5V to 5.5V         |

| to (VCC +0.3V)                              | Operating Temperature          |

| Storage Temperature65°C to +150°C           | HM-6508-5 0°C to +70°C         |

\*CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electrical Specifications** ①

|      |                |                                         | TEMP. 8<br>OPERA<br>RAM | TING     |          | TEST                                                                    |

|------|----------------|-----------------------------------------|-------------------------|----------|----------|-------------------------------------------------------------------------|

|      | SYMBOL         | PARAMETER                               | MIN                     | МАХ      | UNITS    | CONDITIONS                                                              |

|      | ICCSB          | Standby Supply Current                  |                         | 100      | μΑ       | IO = 0<br>VI = VCC or GND                                               |

|      | ICCOP          | Operating Supply Current                |                         | 4        | mA       | Ē = 1MHz, IO = 0<br>VI = VCC or GND                                     |

|      | ICCDR          | Data Retention Supply Current           |                         | 100      | μΑ       | VCC = 2.0, IO = 0<br>VI = VCC or GND                                    |

| D.C. | VCCDR          | Data Retention Supply Voltage           | 2.0                     |          | v        | Ē = VCC                                                                 |

|      | 11             | Input Leakage Current                   | -1.0                    | +1.0     | μΑ       | VI = VCC or GND                                                         |

|      | IOZ            | Output Leakage Current                  | -1.0                    | +1.0     | μΑ       | VO = VCC or GND                                                         |

|      | VIL            | Input Low Voltage                       | -0.3                    | 0.8      | v        |                                                                         |

|      | VIH            | Input High Voltage                      | VCC -2.0                | VCC +0.3 | Ŷ        |                                                                         |

|      | VOL            | Output Low Voltage                      |                         | 0.4      | v        | IO = 1.6mA                                                              |

|      | <b>VOH</b>     | Output High Voltage                     | 2.4                     |          | v        | 10 = -0.2mA                                                             |

|      | CI             | Input Capacitance ③                     |                         | 6        | рF       | VI = VCC or GND<br>f = 1MHz                                             |

|      | со             | Output Capacitance ③                    |                         | 10       | pF       | VO = VCC or GND<br>f = 1MHz                                             |

|      | TELQV          | Chip Enable Access Time                 |                         | 300      | ns       | (4)                                                                     |

|      | TAVQV          | Address Access Time                     |                         | 310      | ns       | (4)<br>(4)                                                              |

|      | TELOX          | Chip Enable Output Enable Time          | 20                      | 200      | ns       | 34                                                                      |

|      | TWLQZ          | ble Time، Write Enable Output Di        |                         | 200      | ns       | 34                                                                      |

|      | TEHQZ          | Chip Enable Output Disable Time         |                         | 200      | ns       | 34                                                                      |

|      | TELEH          | Chip Enable Pulse Negative Width        | 300                     |          | ns       | (4)                                                                     |

| A.C. | TEHEL          | Chip Enable Pulse Positive Width        | 150                     |          | ns       | (4)                                                                     |

| A.C. | TAVEL<br>TELAX | Address Setup Time<br>Address Hold Time | 10<br>70                |          | ns<br>ns |                                                                         |

|      | TDVWH          | Data Setup Time                         | 130                     |          | ns       | 4                                                                       |

|      | TWHDX          | Data Hold Time                          | 0                       |          | ns       | (†<br>(4)                                                               |

|      | TWLEH          | Chip Enable Write Pulse Setup Time      | 160                     |          | ns       | 3<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4) |

|      | TELWH          | Chip Enable Write Pulse Hold Time       | 160                     |          | ns       | ă                                                                       |

|      | TWLWH          | Write Enable Pulse Width                | 160                     |          | ns       | ā                                                                       |

|      | TELEL          | Read or Write Cycle Time                | 450                     |          | ns       | ā                                                                       |

NOTES: (1) All devices tested at worst case temperature and V<sub>CC</sub>.

② Operating supply current (ICCOP) is proportional to operating frequency. Example: typical ICCOP = 1.5mA/MHz.

③ Tested at initial design and after major design changes.

Input rise and fall times: 20ns max. Input and output timing reference level: 1.5V. Output load: 1 TTL gate equivalent and C<sub>L</sub> = 50 to 300pF. For C<sub>L</sub> greater than 50pF, access time is derated 0.15ns/pF. 2

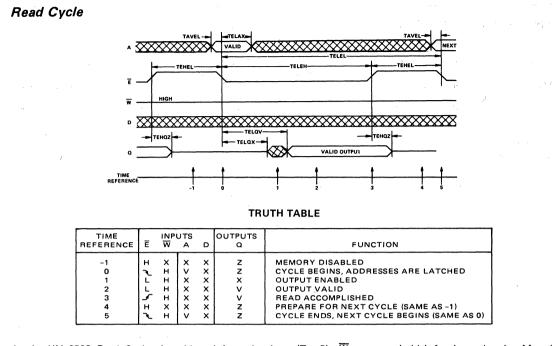

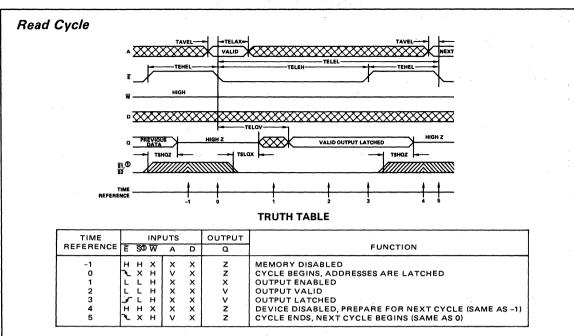

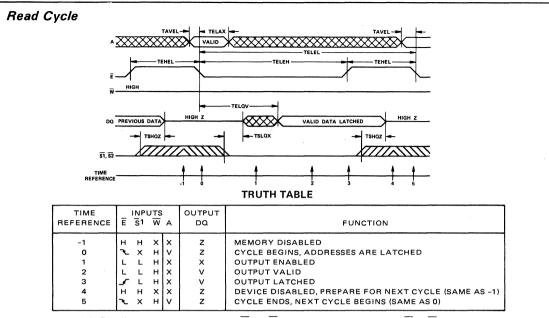

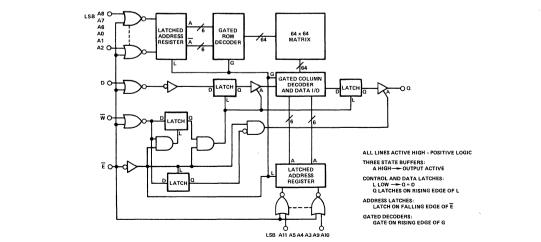

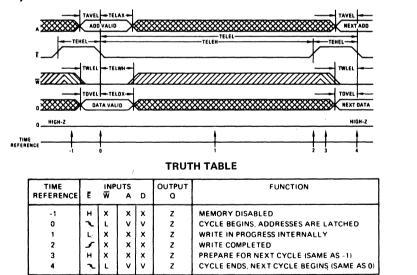

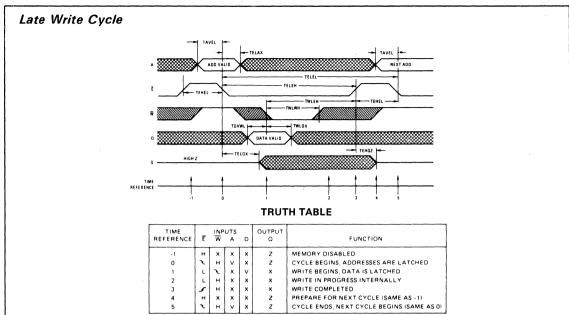

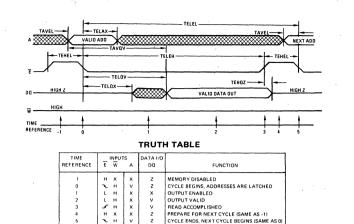

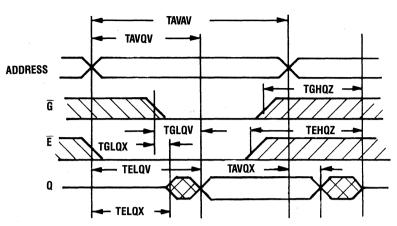

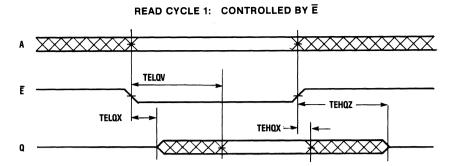

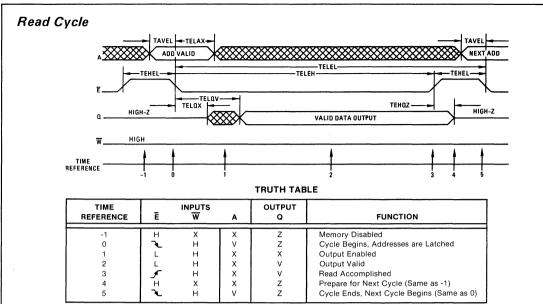

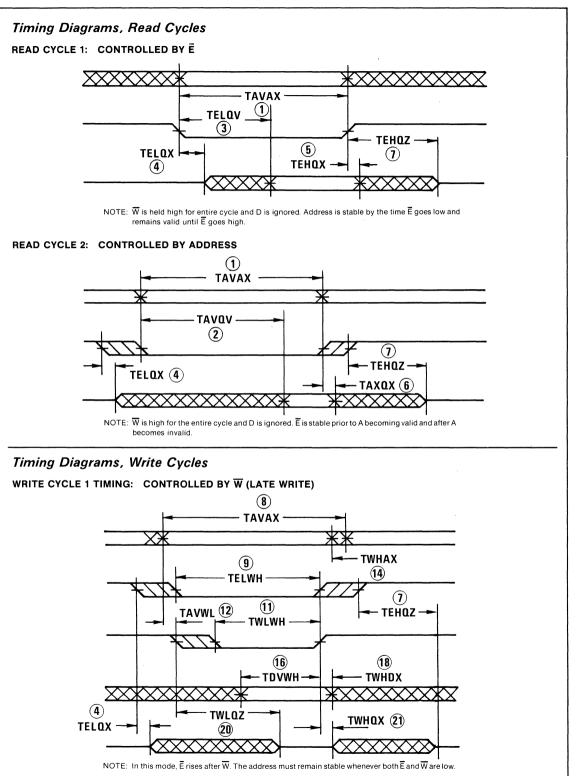

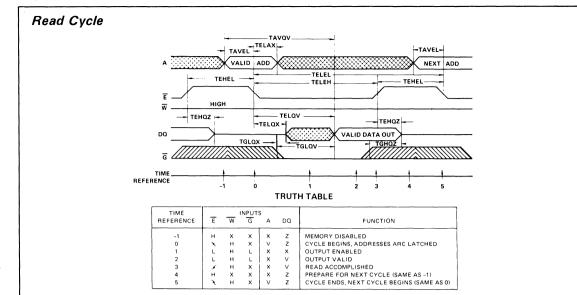

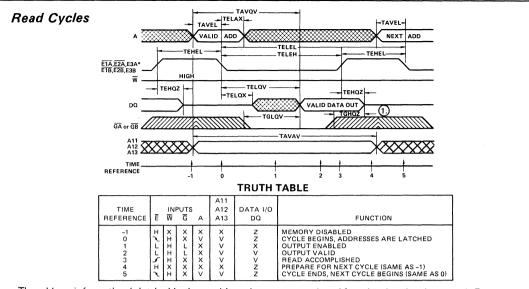

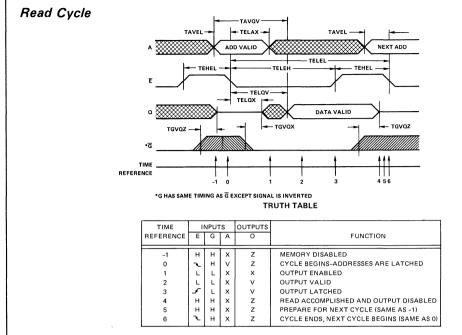

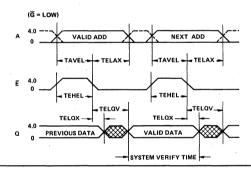

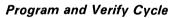

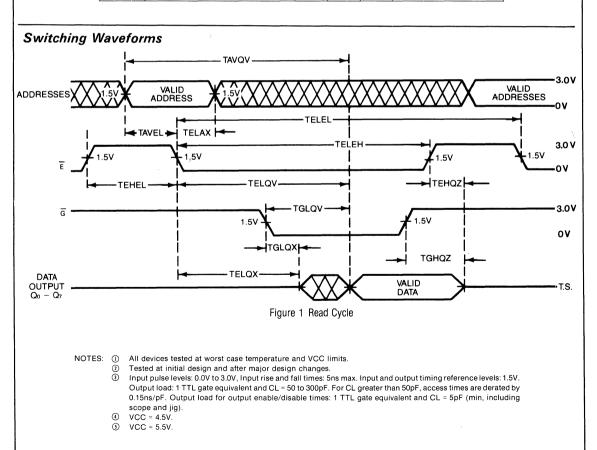

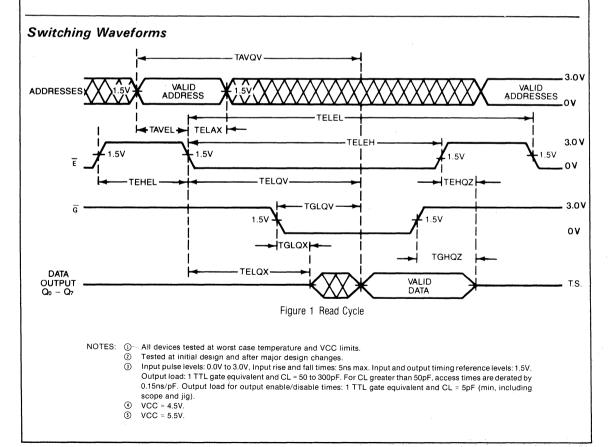

In the HM-6508 Read Cycle, the address information is latched into the on chip registers on the falling edge of  $\overline{E}$  (T = 0). Minimum address setup and hold time requirements must be met. After the required hold time, the addresses may change state without affecting device operation. During time (T = 1) the data output becomes enabled; however, the data is not valid until during time

(T = 2).  $\overline{W}$  must remain high for the read cycle. After the output data has been read,  $\overline{E}$  may return high (T = 3). This will disable the chip and force the output buffer to a high impedance state. After the required  $\overline{E}$  high time (TEHEL) the RAM is ready for the next memory cycle (T = 4).

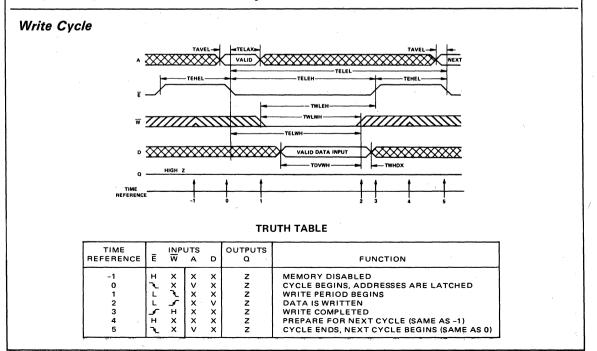

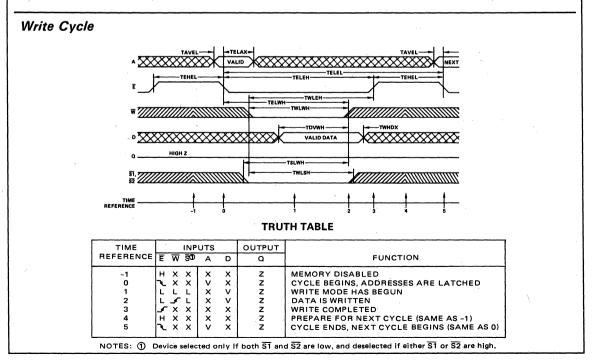

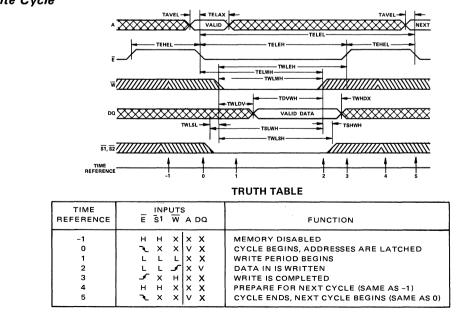

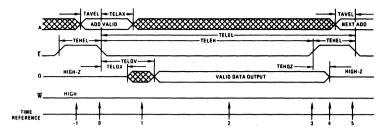

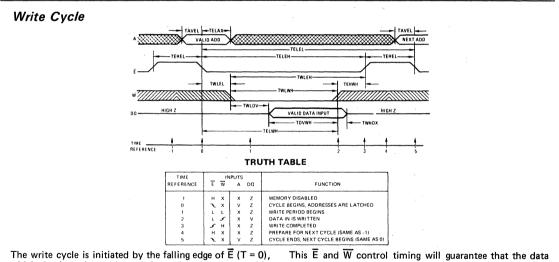

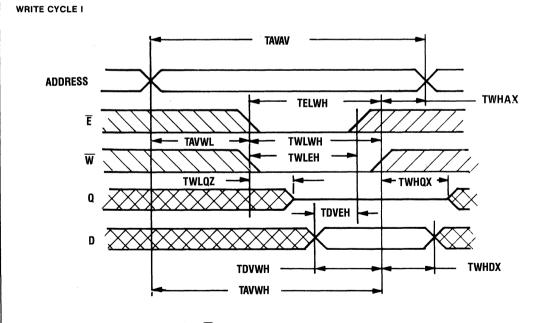

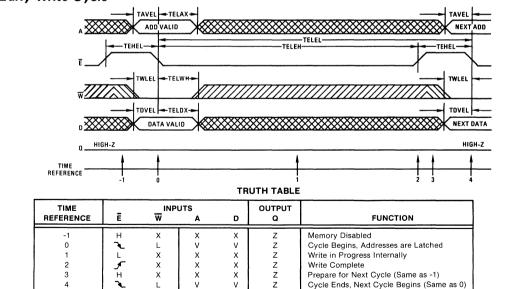

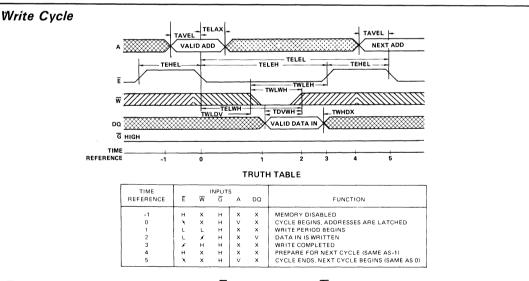

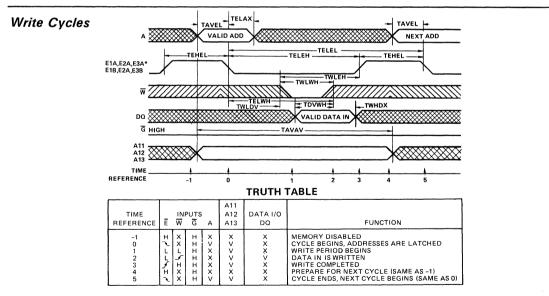

The write cycle is initiated by the falling edge of  $\overline{E}$  which latches the address information into the on chip registers. The write portion of the cycle is defined as both  $\overline{E}$  and  $\overline{W}$  being low simultaneously.  $\overline{W}$  may go low anytime during the cycle provided that the write enable pulse setup time (TWLEH) is met. The write portion of the cycle is terminated by the first rising edge of either  $\overline{E}$  or  $\overline{W}$ . Data setup and hold times must be referenced to the terminating signal.

If a series of consecutive write cycles are to be performed, the  $\overline{W}$  line may remain low until all desired locations have been written. When this method is used, data setup and hold times must be referenced to the rising edge of  $\overline{E}$ . By positioning the  $\overline{W}$  pulse at different times within the  $\overline{E}$  low time (TELEH), various types of write cycles may be performed.

If the  $\bar{E}$  low time (TELEH) is greater than the  $\overline{W}$  pulse (TWLWH) plus an output enable time (TELQX), a combination read write cycle is executed. Data may be modified an indefinite number of times during any write cycle (TELEH). The data input and data output pins may be tied together for use with a common I/O data bus structure. When using the RAM in this method allow a minimum of one output disable time (TWLQZ) after  $\overline{W}$  goes low before applying input data to the bus. This will insure that the output buffers are not active.

# HM-6518

Pinout

TOP VIEW

51 1

Ē 🛛 2

A0 🛛 3

A2 🕇 5

A3 [

А4 Г

٩Ľ

GND

- ADDRESS INPLIT

A0 A1 A2

A3 A4 A5 A6 A7 A8

Δ¢

- CHIP ENABLE

- CHIP SELECT

AF

ē

AI

## 1024 x 1 CMOS RAM

18 VCC

17 1 52

16 D

15 H ₩

14 A9

13 A8

12 A7

11 A6

10 A5

Logic Symbol

W-WRITE ENABLE

Q - DATA OUTPUT

D - DATA INPUT

D

o

#### Features

- HM-6100 Compatible

- Low Operating Power ...... 20mW/MHz Max.

- Fast Access Time ...... 180nsec Max.

- Data Retention Voltage......2.0 Volts Min.

- TTL Compatible In/Out

- High Output Drive 2 TTL Loads

- High Noise Immunity

- On Chip Address Register

- Two Chip Selects for Easy Array Expansion

- Three-State Outputs

- Wide Operating Temperature Ranges:

- ► HM-6518-5.....0°C to +70°C

- ► HM-6518-9.....--40°C to +85°C

- ► HM-6518-2/-8......-55°C to +125°C

#### Description

The HM-6518 is a 1024 by 1 static CMOS RAM fabricated using selfaligned silicon gate technology. Synchronous circuit design techniques are employed to achieve high performance and low power operation.

On chip latches are provided for address and data outputs allowing efficient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays.

The HM-6518 is a fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are guaranteed over temperature.

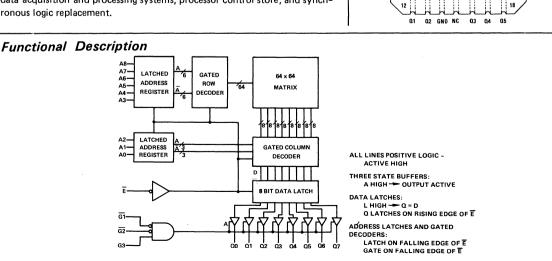

#### Functional Diagram

#### **Operating Range** ~

| Supply Voltage - (VCC - GND)0.3V to +8.0V   |

|---------------------------------------------|

| Input or Output Voltage Applied (GND -0.3V) |

| to (VCC +0.3V)                              |

| Storage Temperature65°C to +150°C           |

| Operating Supply Voltage - VCC |                |

|--------------------------------|----------------|

| HM-6518B-2/-8                  |                |

| HM-6518B-9                     |                |

| Operating Temperature          |                |

| HM-6518B-2/-8                  | 55°C to +125°C |

| HM-6518B-9                     | 40°C to +85°C  |

\*CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electrical Specifications** ①

|      |            |                                           | TEMP. 8<br>OPERA<br>RAM |               |         | TEST                                                              |

|------|------------|-------------------------------------------|-------------------------|---------------|---------|-------------------------------------------------------------------|

|      | SYMBOL     | PARAMETER                                 | MIN                     | MAX           | UNITS   | CONDITIONS                                                        |

|      | ICCSB      | Standby Supply Current                    |                         | 10            | μΑ      | IO = 0<br>VI = VCC or GND                                         |

|      | ICCOP      | Operating Supply Current ②                |                         | 4             | mA      | $\overline{E}$ = 1MHz, IO = 0<br>VI = VCC or GND                  |

|      | ICCDR      | Data Retention Supply Current             |                         | 5             | μΑ      | VCC = 2.0, IO = 0<br>VI = VCC or GND                              |

|      | VCCDR      | Data Retention Supply Voltage             | 2.0                     |               | v       | Ē = VCC                                                           |

|      | 11         | Input Leakage Current                     | -1.0                    | +1.0          | μΑ      | VI = VCC or GND                                                   |

| D.C. | IOZ        | Output Leakage Current                    | -1.0                    | +1.0          | μΑ      | VO = VCC or GND                                                   |

|      | VIL        | Input Low Voltage                         | -0.3                    | 0.8           | v       |                                                                   |

|      | VIH        | Input High Voltage                        | VCC -2.0                | VCC +0.3      | v       |                                                                   |

|      | VOL        | Output Low Voltage                        |                         | 0.4           | v       | 10 = 3.2mA                                                        |

|      | <b>VOH</b> | Output High Voltage                       | 2.4                     |               | v       | 10 = -0.4mA                                                       |

|      | CI         | Input Capacitance ③                       |                         | 6             | pF      | VI = VCC or GND<br>f = 1MHz                                       |

|      | со         | Output Capacitance ③                      |                         | 10            | pF      | VO= VCC or GND<br>f = 1MHz                                        |

|      | TELQV      | Chip Enable Access Time                   |                         | 180           | ns      |                                                                   |

|      | TAVQV      | Address Access Time                       |                         | 180           | ns      | (4)<br>(3)<br>(4)                                                 |

|      | TSLOX      | Chip Select Output Enable Time            | 20                      | 120           | ns      | രമ്                                                               |

|      | TWLOZ      | Write Enable Output Disable Time          | 20                      | 120           | ns      | ää                                                                |

|      | TSHOZ      | Chip Select Output Disable Time           |                         | 120           | ns      | ää                                                                |

|      | TELEH      | Chip Enable Pulse Negative Width          | 180                     |               | ns      | Ĩ                                                                 |

|      | TEHEL      | Chip Enable Pulse Positive Width          | 100                     |               | ns      | ă                                                                 |

| A.C. | TAVEL      | Address Setup Time                        | 0                       |               | ns      | ă.                                                                |

| A.C. | TELAX      | Address Hold Time                         | 40                      |               | ns      | 4                                                                 |